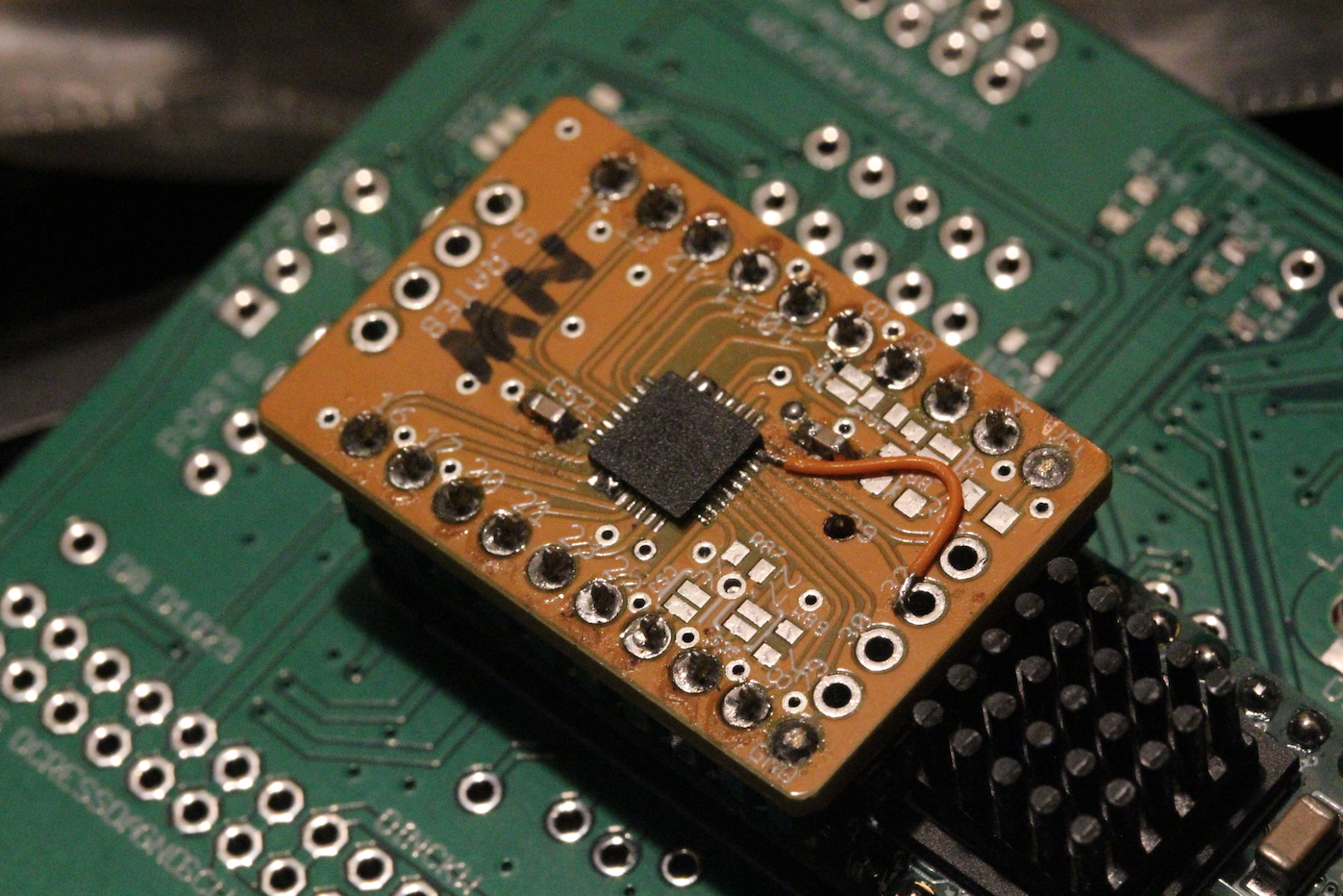

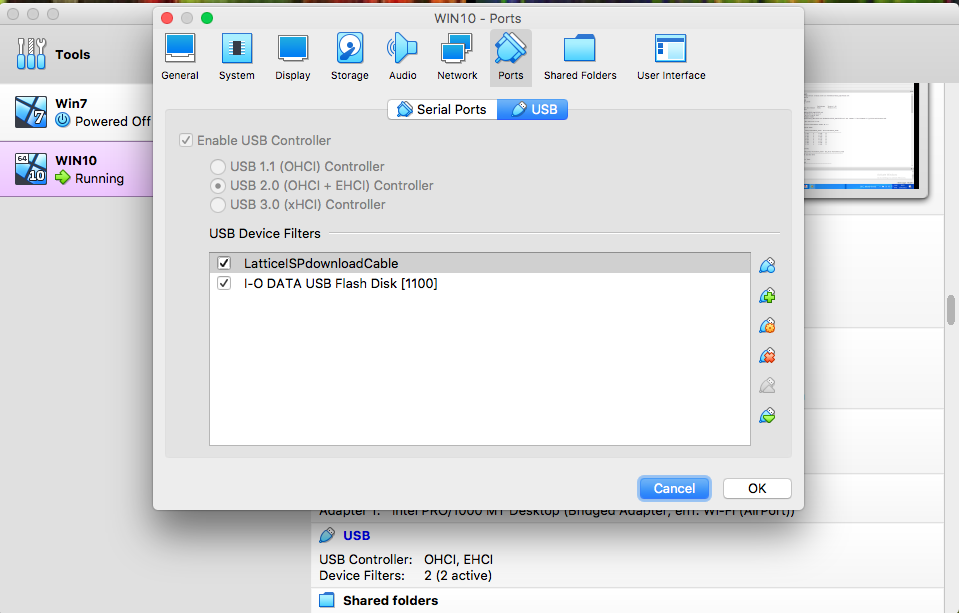

I measured the resistance between the corresponding JTAG port/device on the FPGA board, which was suspected to be broken due to the hole made to access the reset pin of Teensy4.1, and found a delicate value of 40mΩ. Initially, we tried to write the device as it was, but failed to verify it after writing.

Unfortunately, the semi-disconnected state was confirmed, so the firmware was rewritten after ensuring sound continuity with jumper wires.

In the process of piggybacking the FPGA onto the MCU, I found a pin #41 (reset pin) on the top side of the MCU board that I had forgotten to set, so I implemented an additional pin.

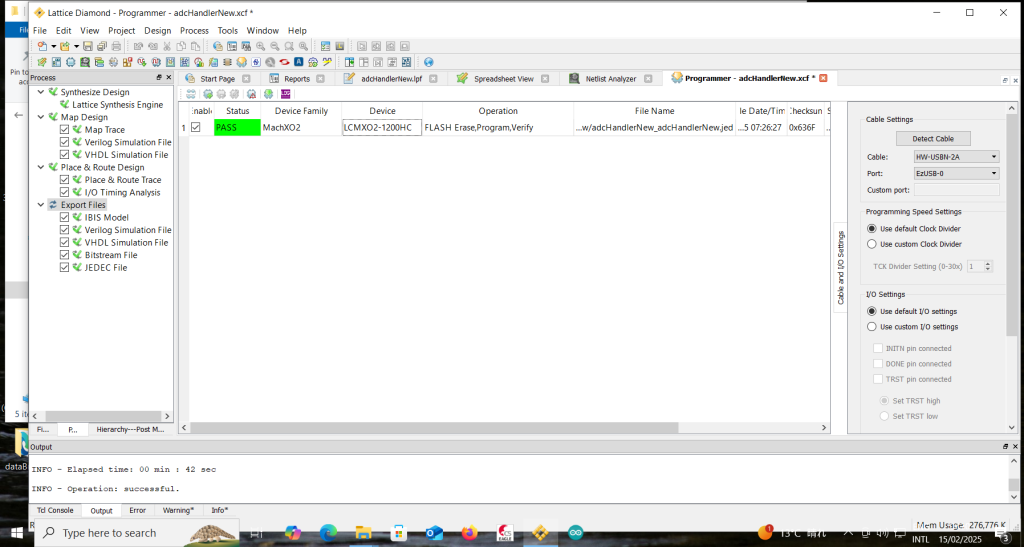

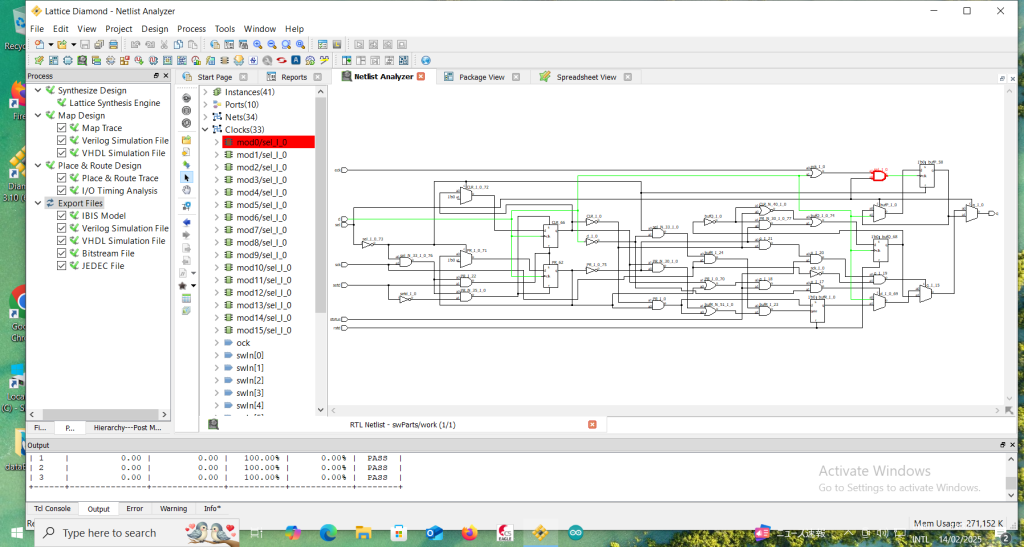

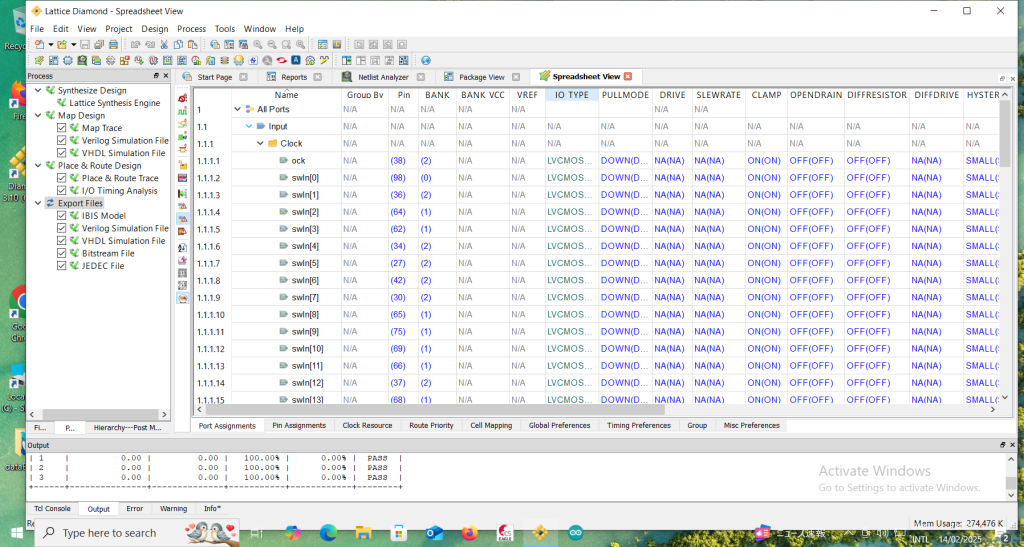

On the other hand, I am preparing to port the Xlinx CPLDs that used to make up the KuwaidanSwitchMatrix to the Lattice/XO2.

I have already completed the logic synthesis and am considering the interior of the clock generator that was set up externally. Pin fitting is incomplete though,

The process of reconfiguring the array may be faulty.

As an alternative approach, we are considering the method of adding more ports to the MCU via I2C connection. The MCU + I2C device configuration is simpler than using an FPGA.